欢迎进入某某教育官方网站!

咨询热线:400-123-4567

GaN互补逻辑电路的构件

由北京大学、北京工业大学、中国科学技术大学和香港科技大学联合而成的团队评论道:“这项研究证明了GaN互补逻辑在兆赫级功率集成电路(PIC)和恶劣环境电子器件方面的潜力。”

GaN互补逻辑性能的一个关键瓶颈是p-沟道FET与成熟n-FET的互补。GaN p-FET的最大漏极电流通常小于10mA/mm。这与镁(Mg)作为电子受体产生正空穴电荷载流子的性能较差有关。

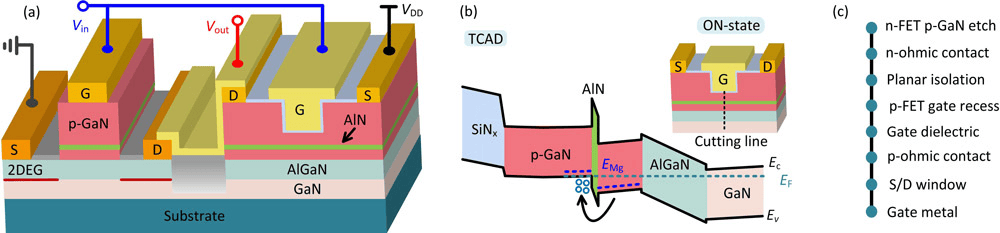

为了解决这一问题,研究人员使用了在p型层中插入氮化铝(AlN)层的外延材料。这就产生了一个电荷极化场,改变了p型层的费米级,从而增强了镁受体的电离。

研究人员解释道:“p-FET的特点是,AlN插入层将受体能级(EMg)推至费米级(EF)以下,因此EMg能级上的空穴会完全电离,并转移到AlN之上。”

图1:(a)GaN互补逻辑(CL)平台方案。(b)导通状态下p-FET栅极区的模拟能带图。(c)工艺流程。

通过刻蚀p型层并利用AlGaN势垒下方形成的n型二维电子气体(2DEG)沟道建立源极/漏极接触,制造出n-FET。用于欧姆接触的退火金属是钛/铝/镍/金(Ti/Al/Ni/Au)。

互补逻辑的p-FET侧是采用凹槽栅极和20nm氮化硅栅极绝缘层制造的。在这种情况下,欧姆源极/漏极接触为退火镍/金。栅极和探针垫的最终金属化为钛/金。

两类器件的栅极都置于源极和漏极之间。p-FET和n-FET的栅极长度分别为2μm和4μm,源极/漏极的相应间距分别为4μm和3μm。

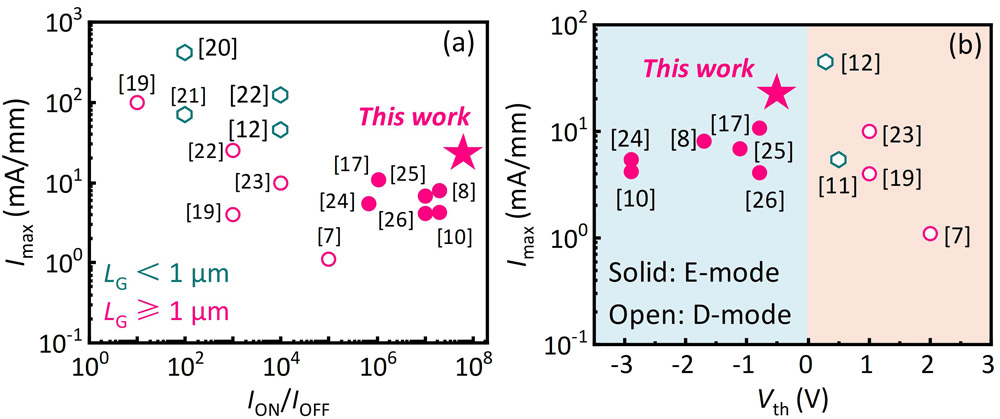

单个p-FET的最大漏极电流为23mA/mm。阈值电压(Vth)为-0.5V,实现了增强(E)型、“常关”工作。导通/关断电流比为6.5x107。亚阈值摆幅为89mV/decade。n-FET也是增强型,阈值电压为+1.3V。

图2:GaN p-FET的基准(不含FinFET和/或三栅FET)。Vth由10μA/mm漏极电流决定,以便进行公平比较。

根据与已发表研究相对比的基准图(图2),研究团队称“在增强型GaN p-FET中,新器件的Imax和ION/IOFF更为出色”。由于研究目标是功率集成电路的部署,该基准排除了FinFET和三栅结构,因为这两类器件的目标是高速/射频性能。

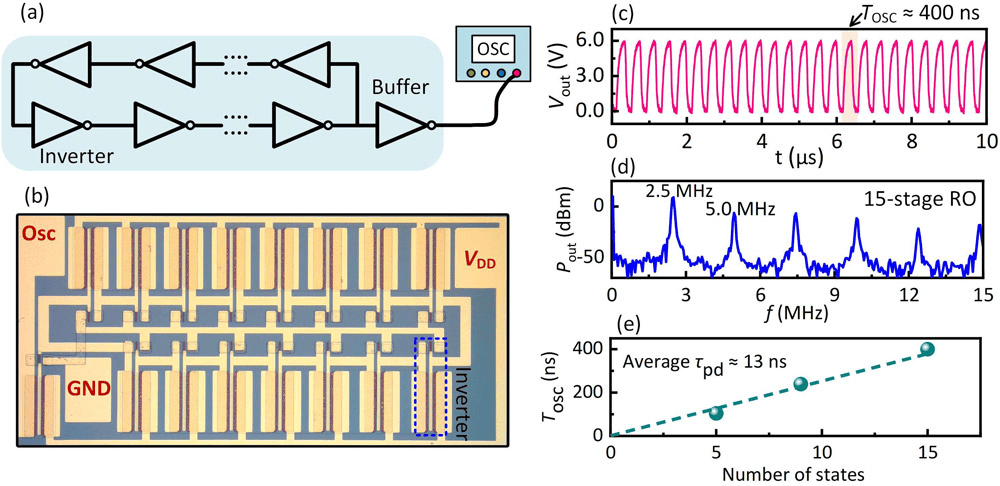

研究人员在不同互补逻辑拓扑结构中测试了他们的器件,其中包括:反相器、传输门/与非门/或非门、RS(复位-置位)锁存器/触发器、带有功率HEMT的缓冲器、环形振荡器。反相器的最大电压增益达到118.9。

图3:(a)与驱动外部负载电阻的功率HEMT单片集成的GaN互补逻辑缓冲器。(b)输入波形和输出波形。

这一互补逻辑缓冲器在6V VDD下工作,这是功率集成电路的典型电压(图3)。该缓冲器用于驱动栅长为17μm的功率HEMT,其增强型的阈值电压为+1.3V。该HEMT的母线V。

研究团队评论道:“合适的开关操作验证了GaN互补逻辑电路用于GaN功率集成电路(PIC)的能力。在大学实验室进行的初步研究中,功率HEMT的栅极宽度仅为100μm。为了演示快速开关操作,需要采用大面积功率HEMT,以最大限度地减少寄生电容的影响,这仍是未来的工作重点。”

图4:(a)环形振荡器电路。(b)15级环形振荡器的显微照片。(c)-(d)15级环形振荡器在VDD = 6V时的电压波形和功率谱,具有约400ns的振荡周期(Tosc)和2.5MHz的基频(fosc)。(e)Tosc与环形振荡器级数(N)的相对关系。

对于环形振荡器电路(图4),研究人员评论道:“本研究中的GaN环形振荡器显示出短至13ns左右的突破性传播延迟τpd,先前发表的研究成果则大于30ns。”

2025年2月26日14:00,《化合物半导体》杂志将联合常州臻晶半导体有限公司给大家带来“碳化硅衬底产业的淘汰赛:挑战与应对之道”的线上主题论坛,共同探索碳化硅衬底产业生存之道,推动我国碳化硅产业的创新发展!诚邀您报名参会:

隶属于ACT雅时国际商讯旗下的两本优秀杂志:《化合物半导体》&《半导体芯科技》2025年研讨会全年计划已出。